Product Summary

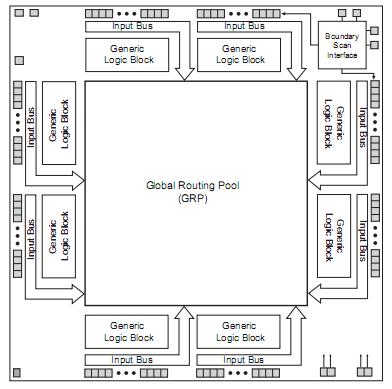

The ISPLSI5256VE125LF256-100I is an In-System Programmable High Density Logic Device. The ISPLSI5256VE125LF256-100I is based on Generic Logic Blocks (GLBs) of 32 registered macrocells and a single Global Routing Pool (GRP) structure interconnecting the GLBs. Outputs from the GLBs drive the Global Routing Pool(GRP) between the GLBs. Switching resources are provided to allow signals in the Global Routing Pool to drive any or all the GLBs in the ISPLSI5256VE125LF256-100I. This mechanism allows fast, efficient connections across the entire device.

Parametrics

ISPLSI5256VE125LF256-100I absolute maximum ratings: (1)Supply Voltage Vcc:-0.5 to +5.4V; (2)Input Voltage Applied:-0.5 to +5.6V; (3)Tri-Stated Output Voltage Applied:-0.5 to +5.6V; (4)Storage Temperature:-65℃ to 150℃; (5)Case Temp. with Power Applied:-55℃ to 125℃; (6)Max. Junction Temp. (TJ) with Power Applied:150℃.

Features

ISPLSI5256VE125LF256-100I features: (1)3.3V Power Supply; (2)User Selectable 3.3V/2.5V I/O; (3)12000 PLD Gates / 256 Macrocells; (4)Up to 144 I/O Pins; (5)256 Registers; (6)High-Speed Global Interconnect; (7)SuperWIDE Generic Logic Block (32 Macrocells) for Optimum Performance; (8)SuperWIDE Input Gating (68 Inputs) for Fast Counters, State Machines, Address Decoders, etc.; (9)PCB Efficient Ball Grid Array (BGA) Package Options; (10)Interfaces with Standard 5V TTL Devices; (11)fmax = 165 MHz Maximum Operating Frequency; (12)tpd = 6.0 ns Propagation Delay; (13)TTL/3.3V/2.5V Compatible Input Thresholds and Output Levels; (14)Electrically Erasable and Reprogrammable; (15)Non-Volatile; (16)Programmable Speed/Power Logic Path Optimization; (17)Enhanced Pin-Locking Architecture with Single-Level Global Routing Pool and SuperWIDE GLBs; (18)Wrap Around Product Term Sharing Array Supports up to 35 Product Terms Per Macrocell; (19)Macrocells Support Concurrent Combinatorial and Registered Functions; (20)Macrocell Registers Feature Multiple Control Options Including Set, Reset and Clock Enable; (21)Four Dedicated Clock Input Pins Plus Macrocell Product Term Clocks.

Diagrams

|

ISPL1048E-50LQ. |

Other |

|

Data Sheet |

Negotiable |

|

||||||||

|

ispLSi 1016 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||

|

ispLSI 1016-110LJ |

Lattice |

CPLD - Complex Programmable Logic Devices USE ispMACH 4000V |

Data Sheet |

|

|

||||||||

|

ispLSI 1016-60LJ |

Lattice |

CPLD - Complex Programmable Logic Devices USE ispMACH 4000V |

Data Sheet |

|

|

||||||||

|

ispLSI 1016-60LJI |

Lattice |

CPLD - Complex Programmable Logic Devices USE ispMACH 4000V |

Data Sheet |

|

|

||||||||

|

ispLSI 1016-60LT44 |

Lattice |

CPLD - Complex Programmable Logic Devices USE ispMACH 4000V |

Data Sheet |

|

|

||||||||

(China (Mainland))

(China (Mainland))